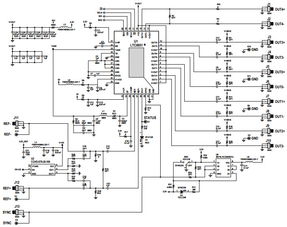

基于LTC6951的5输出整数N PLL集成VCO的参考设计 DC2248A-A演示板详解

在高速通信、测试测量和雷达系统中,高性能、低噪声的时钟生成与分配至关重要。LTC6951作为一款先进的整数N分频锁相环(PLL)芯片,集成了压控振荡器(VCO),能够提供多个超低抖动、高精度的同步时钟输出。与之配套的DC2248A-A演示板,则为工程师提供了一个功能完整、易于评估和快速原型开发的参考设计平台。本文将深入探讨该演示板的设计理念、核心芯片特性及其在集成电路设计服务中的应用价值。

一、核心芯片LTC6951:高性能时钟解决方案的核心

LTC6951是一款由亚德诺半导体(Analog Devices)推出的高性能整数N PLL。其核心优势在于集成了宽带、低噪声的VCO,频率范围覆盖62.5 MHz至2 GHz,无需外部VCO元件,极大地简化了系统设计并节省了电路板空间。芯片支持整数N分频模式,能够根据参考时钟精确合成所需的输出频率。

关键特性包括:

1. 多路超低抖动输出:提供多达5路独立的时钟输出通道(其中4路为LVDS/CMOS可选,1路为固定LVDS)。每路输出均可独立分频和调整相位,相位噪声和抖动性能卓越,尤其适合驱动高速ADC、DAC或作为FPGA的同步时钟源。

2. 集成VCO与环路滤波器:内部集成VCO减少了对外部元件的依赖,降低了设计复杂性和噪声引入点。其灵活的环路滤波器架构允许用户针对不同的相位噪声、锁定时间和参考杂散指标进行优化。

3. 灵活的配置与监控:通过SPI接口可对分频比、输出格式、功率等所有参数进行数字编程。芯片还集成了锁定检测和同步功能,确保多路输出之间精确的相位关系,便于系统同步。

二、DC2248A-A演示板:从评估到集成的桥梁

DC2248A-A演示板是一个经过充分验证的硬件平台,旨在全面展示LTC6951在真实工作环境下的性能。它不仅仅是一块评估板,更是一个完整的参考设计,为工程师提供了可直接借鉴或修改的设计蓝图。

演示板的主要构成与功能:

1. 完整的信号链:板上集成了LTC6951芯片、必要的电源管理电路、高精度参考时钟输入接口(如100MHz OCXO或外部输入)、以及5路时钟输出的连接器(通常为SMA接口),构成了一个立即可工作的时钟生成系统。

2. 直观的配置与测试:板载的USB接口可通过配套软件(如ADI的PLLWizard)连接电脑,实现图形化参数配置和实时性能监控。工程师可以轻松测试不同频点、分频比下的相位噪声、抖动和锁定时间,加速设计决策。

3. 优化的布局与布线:演示板的PCB布局严格遵循高速、低噪声设计原则,例如为PLL内核和输出缓冲器提供独立的低噪声电源层、优化去耦电容布局、控制传输线阻抗等。这些细节是保证芯片达到标称性能的关键,为用户的自主设计提供了宝贵的参考。

三、在集成电路芯片设计及服务中的应用

对于提供集成电路设计及服务的企业或团队而言,LTC6951和DC2248A-A演示板的价值体现在多个层面:

- 加速客户系统开发:在为客户提供定制化系统解决方案时,尤其是涉及高速数据采集、相控阵雷达或多通道同步测试设备时,可以直接推荐或采用此成熟方案。利用演示板进行快速原型验证,能显著缩短客户的研发周期,降低技术风险。

- 作为内部设计的性能标杆:在进行自主时钟芯片或包含时钟模块的SoC设计时,LTC6951的架构和性能参数可以作为重要的设计参考和验证基准。DC2248A-A的布局布线经验,对于提升自身芯片的板级应用性能具有直接的指导意义。

- 提供增值技术服务:设计服务团队可以基于该平台,为客户提供更深入的时钟树设计、抖动分析、系统同步方案优化等专业服务。演示板成为了一个强大的演示和调试工具,增强了服务的专业性和说服力。

- 教学与培训:该平台也是培训新工程师理解高性能PLL系统设计、噪声分析和PCB布局技术的绝佳实物教材。

结论

LTC6951集成VCO的整数N PLL与DC2248A-A演示板的组合,代表了一个经过生产验证的高端时钟解决方案。它通过高度集成的芯片设计和精心优化的参考硬件,将复杂的时钟系统设计转化为可快速部署的工程实践。对于任何致力于高性能电子系统开发的工程师或集成电路设计服务提供商而言,深入理解和利用这一参考设计,无疑是提升产品竞争力、确保系统时序性能并加速项目上市进程的有效途径。从评估评估到最终产品集成,DC2248A-A演示板架起了一座从理论到可靠实现的坚实桥梁。

如若转载,请注明出处:http://www.yiyunping.com/product/84.html

更新时间:2026-04-06 02:23:08