集成电路设计视图 芯片设计的核心流程与专业服务

集成电路(IC)是现代电子设备的“大脑”,其设计过程复杂而精密,通常以“设计视图”为核心框架展开。集成电路设计视图是一个分层抽象的概念体系,它将芯片从概念到实物的实现过程,分解为多个逻辑层次和物理层次,每一层都有其特定的设计目标、工具和方法。而围绕这一核心流程,衍生出了庞大且专业的集成电路芯片设计及服务产业,共同推动着半导体技术的持续创新。

一、集成电路设计视图:从抽象到实物的层级架构

集成电路设计遵循“自顶向下”的设计方法,通过不同层级的“视图”来管理和实现复杂功能。主要视图包括:

- 系统架构视图:这是最高层级的抽象。设计者在此定义芯片的整体功能、性能指标、功耗预算、以及与其他系统组件的接口(如处理器内核、内存控制器、专用加速模块等)。它关注的是“做什么”。

- 寄存器传输级(RTL)视图:这是数字电路设计的核心。设计人员使用硬件描述语言(如Verilog或VHDL),将系统架构描述为时钟沿触发的寄存器之间数据传输的逻辑。这一层级定义了芯片的精确行为,是后续逻辑综合的基础。

- 逻辑门级视图:通过逻辑综合工具,将RTL代码自动映射到标准单元库(如与门、或门、触发器等)构成的门级网表。此视图关注逻辑功能的正确性和时序。

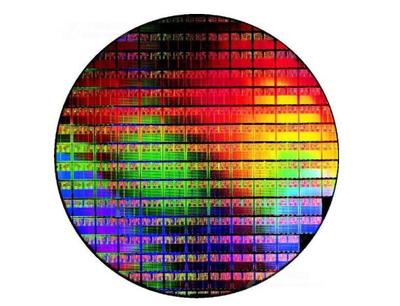

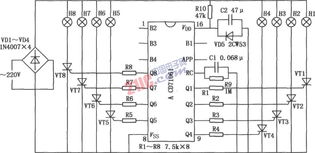

- 物理设计视图:这是将逻辑网表转化为实际几何图形的过程,也称为“后端设计”。它包括布局(确定每个单元在芯片上的位置)、布线(用金属线连接各个单元)、时序收敛(确保信号在指定时钟频率下稳定)和物理验证(检查设计规则、电学特性等)。最终输出用于芯片制造的GDSII文件。

- 晶体管级视图:对于模拟电路或高性能数字单元(如存储器、锁相环),设计需要在晶体管级别进行。这涉及到单个MOSFET的尺寸、偏置和互连,对设计者的模拟电路功底要求极高。

这些视图相互关联,层层递进,构成了芯片设计的完整生命周期。

二、集成电路芯片设计服务:专业分工与生态协作

随着工艺节点不断微缩(如进入5纳米、3纳米),设计复杂度、成本和风险呈指数级增长。因此,除了拥有完整设计能力的大型IDM(集成器件制造商,如英特尔)或Fabless公司(无晶圆厂设计公司,如高通、英伟达)外,一个高度专业化的设计服务生态应运而生。主要服务包括:

- IP核授权与集成服务:知识产权核是预先设计好的、经过验证的功能模块(如ARM处理器内核、接口协议IP等)。设计服务公司提供成熟IP的授权,并帮助客户将其高效集成到自己的芯片设计中,极大缩短开发周期。

- 设计实现与外包服务:许多公司,特别是初创企业,可能只专注于架构定义和RTL设计,而将后续耗资巨大的逻辑综合、物理设计、验证和流片准备等工作,外包给专业的设计服务公司。这些公司拥有经验丰富的工程师团队和先进的EDA工具,能有效应对物理设计中的各种挑战。

- 定制化设计与全流程服务:针对特定应用(如人工智能、汽车电子、物联网),服务商提供从规格定义、架构探索、前后端设计到流片、封装测试的“交钥匙”解决方案。这对于缺乏完整设计团队或想快速进入新领域的客户至关重要。

- 云上EDA与设计平台服务:基于云计算的设计平台正成为趋势。服务商提供在云端部署的EDA工具链、计算资源和协同设计环境,使设计团队可以灵活获取海量算力进行仿真验证,并实现远程协作,降低了软硬件投入门槛。

三、挑战与未来展望

当前,集成电路设计面临着工艺逼近物理极限、功耗墙、设计成本飙升等多重挑战。先进封装(如Chiplet/小芯片)技术正在改变设计视图的边界,系统级设计需要统筹考虑多个异质芯片的集成。未来的设计服务将更加注重:

- 系统-芯片协同优化:在更高层次上进行软硬件联合设计与验证。

- AI驱动的设计自动化:利用机器学习加速布局布线、功耗优化和验证过程。

- 面向特定领域的设计:为AI、汽车、高性能计算等垂直领域提供深度优化的架构和IP解决方案。

###

集成电路设计视图是指导芯片从蓝图变为现实的科学方法论,而蓬勃发展的芯片设计服务产业则是将方法论转化为生产力的关键支撑。两者相辅相成,共同构成了全球半导体创新的基石。随着技术演进和市场需求变化,这一领域的专业分工与协作将愈发深入,持续驱动着信息技术的革新与发展。

如若转载,请注明出处:http://www.yiyunping.com/product/64.html

更新时间:2026-04-15 06:56:47